# HIGH SPEED DATA PRODUCTS IC Handbook

# **Foreword**

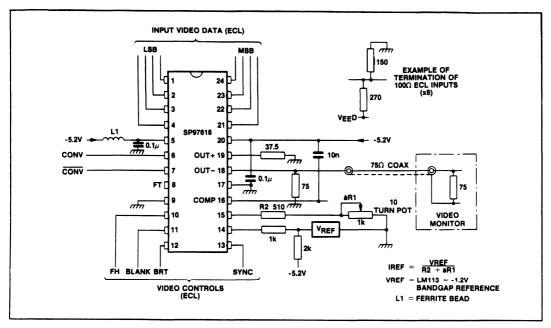

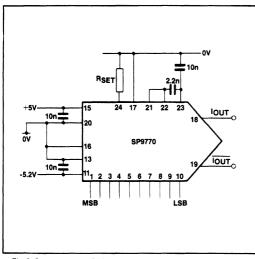

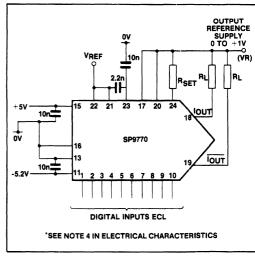

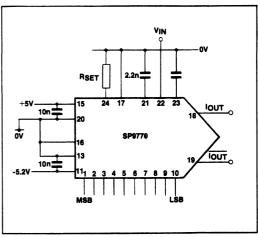

Plessey Semiconductors has long been recognised as a leading source of high speed data conversion ICs. Our renowned **SP9600** series comparators led to the development of 4-bit and 6-bit ADCs capable of conversion rates in excess of 100MHz. Alongside these the awardwinning **SP9768** 150MHz 8-bit DAC set the scene for the 10-bit **SP9770** and the even faster **SP97618** 250MHz 8-bit Graphics DAC.

There are four new ADCs all offering 8-bit resolution with conversion rates ranging from the 20MHz **SP94308** Video System ADC through to the flagship **SP97508** which guarantees 100MHz operation. We are also launching video speed CMOS DACs with graphics controls and a stunning 450MHz 8-bit DAC which is ideal for waveform synthesis and frequency-agile communication systems. Perhaps most impressive of all is a range of subnanosecond comparators in dual, quad and octal configurations, all featuring glitch capture and adjustable hysteresis. And supporting this rapidly growing range of data conversion products are the recently introduced **SL9999** ADC driver and now the **SP92701** 700MHz line receiver/driver.

The range of **64 word** FIFOs now provides for both cascade and standalone requirements with a range of guaranteed operating frequencies from 10MHz to 35MHz.

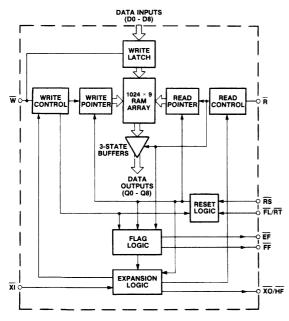

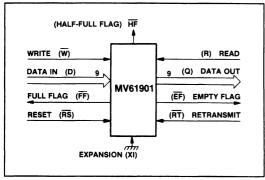

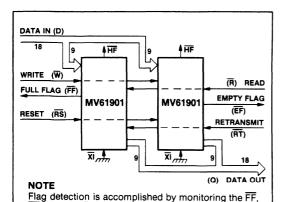

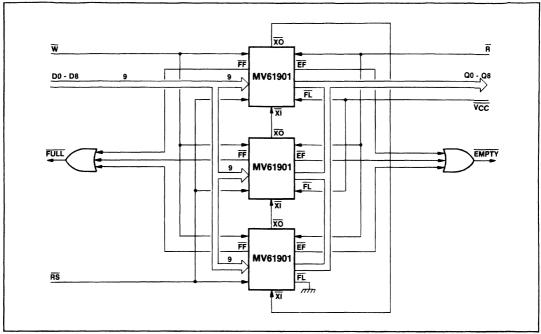

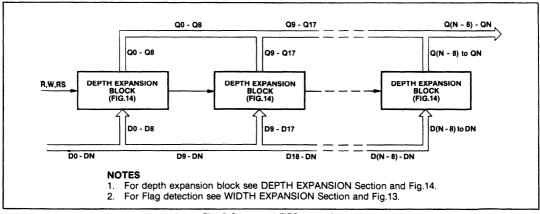

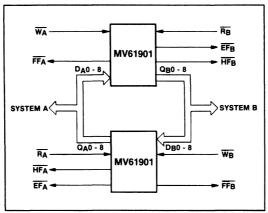

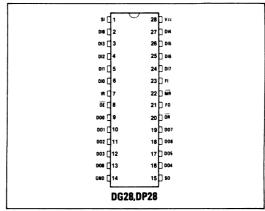

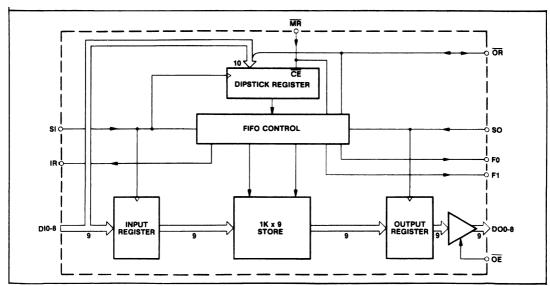

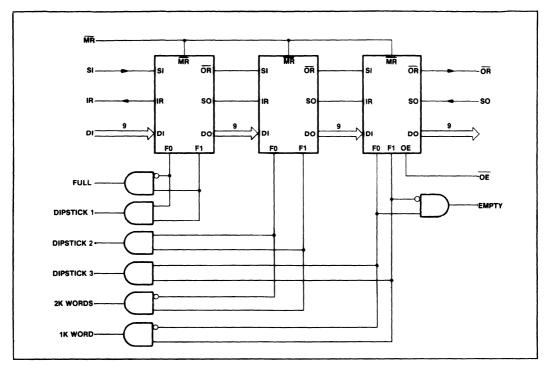

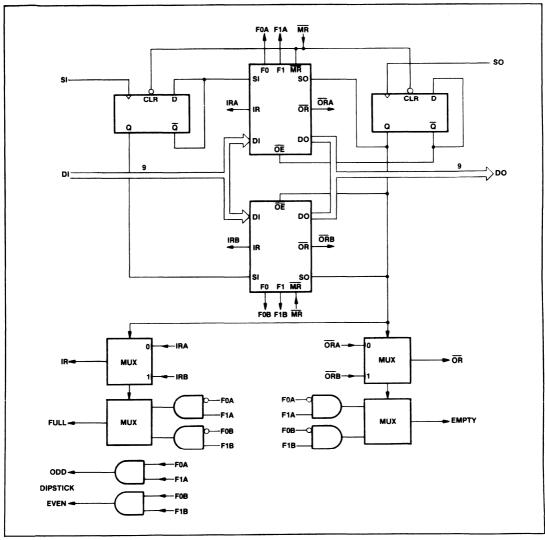

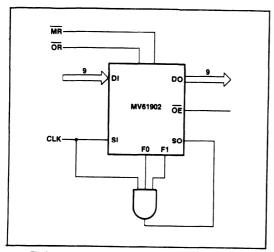

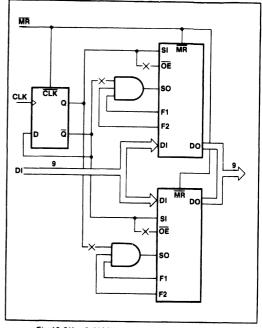

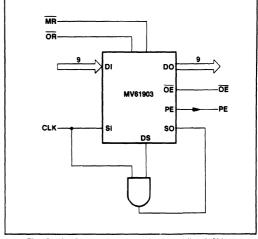

Three **1K word** by 9-bit FIFOs are being introduced: the **MV61901** offers pin and function compatibility with existing industry standard parts while the **MV61902** and **MV61903** provide tremendous applications advantages with the programmable flag (DIPSTICK) and PARITY features. The DIPSTICK FIFO allows users to design programmable delay lines with just a single AND gate while the PARITY FIFO offers parity checking and generation circuits that give value for money in their own right.

The 50MBit Fibre Optic circuits are generating interest worldwide especially since the Manchester encoding/decoding techniques employed ensure clock and data integrity. Not content with this Plessey Semiconductors now have available samples of three 200MBit chips: an LED driver (SP9954), Transimpedance Amplifier (SL9904) and a Dataslice (SP9944).

# **Contents**

|                                           | Page |

|-------------------------------------------|------|

| Foreword                                  | 2    |

| Product index                             | 4    |

| Product list - alpha numeric              | 8    |

| Semi-custom design                        | 10   |

| The Quality Concept                       | 12   |

| Technical data                            |      |

| 1. Data communications                    | 15   |

| 2. Data conversion                        | 43   |

| 3. Specialised memory products            | 149  |

| 4. High speed logic                       | 225  |

| Applications information                  | 273  |

| Package outlines and ordering information | 281  |

| Placeay Semiconductors locations          | 200  |

# Product index - Data communications

## Data Control and Automation

|         | Function                            |                                  |    |      |    |

|---------|-------------------------------------|----------------------------------|----|------|----|

| MV60011 | HDLC/DMA controller (e.g. for ISDN) | 128Kbits/s (data),<br>8MHz (DMA) | 5V | CMOS | 17 |

| MV6101  | Dual quadrature counter             | 10MHz                            | 5V | CMOS | 26 |

<sup>1</sup> Manufactured under licence from British Telecom

## Fibre Optics/LAN/High Speed Serial Data

| Type   | Sunction Supplemental Control of the | La la companya da la<br>La companya da la co | Superior<br>Valuati | Process<br>Constant |    |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|----|

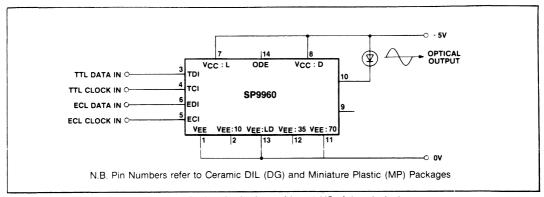

| SP9960 | Encoder/LED driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50M bit                                                                                                                                                                                                                          | +5V or -5.2V        | Bipolar             | 29 |

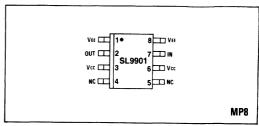

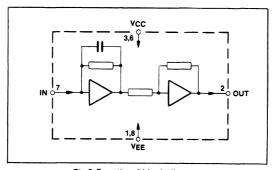

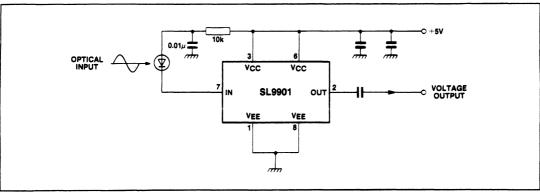

| SL9901 | Trans-impedance amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 50MHz                                                                                                                                                                                                                            | +5V or -5.2V        | Bipolar             | 34 |

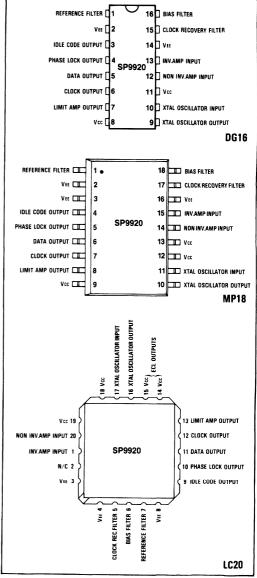

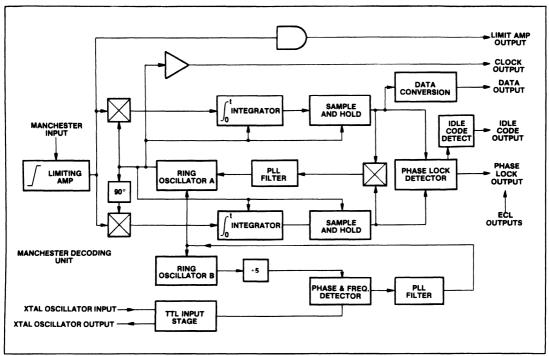

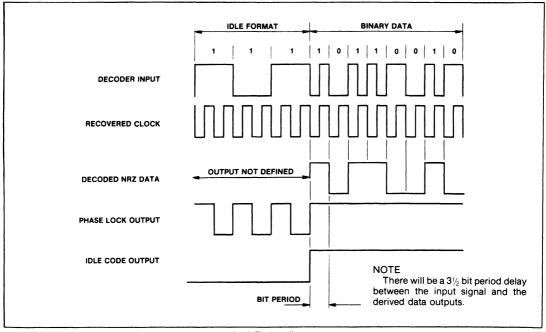

| SP9920 | Manchester decoder with idle code detect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50M bit                                                                                                                                                                                                                          | +5V or -5.2V        | Bipolar             | 36 |

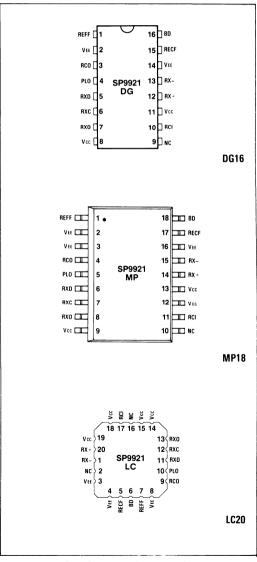

| SP9921 | Manchester biphase-mark decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5M bit                                                                                                                                                                                                                           | +5V or -5.2V        | Bipolar             | 39 |

# Product index - Data conversion

# Analog to Digital converters

| Troe     | Function Provide Providence (Co.)             | Darwije d Ciletinu<br>Gook Rais | A PLACED L | Page |

|----------|-----------------------------------------------|---------------------------------|------------|------|

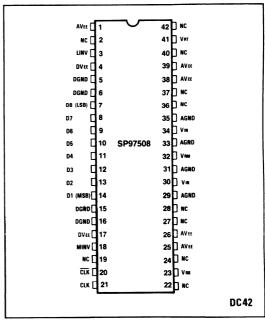

| SP97508  | 8-bit flash ADC                               | 110MHz                          | Bipolar    | 45   |

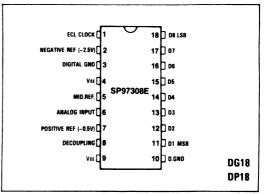

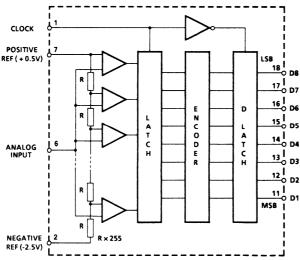

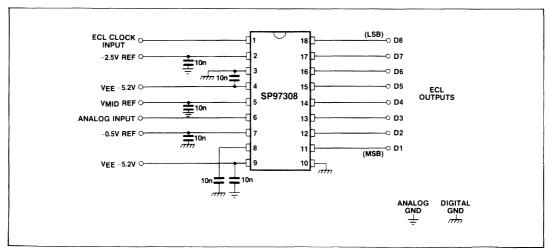

| SP97308E | 8-bit flash ADC, ECL outputs                  | 30MHz                           | Bipolar    | 51   |

| SP97308T | 8-bit flash ADC, TTL/CMOS outputs             | 30MHz                           | Bipolar    | 54   |

| SP94308  | 8-bit video system ADC                        | 20MHz                           | Bipolar    | 58   |

| SP97561  | 6-bit wide input bandwidth ADC (250MHz - 3dB) | 110MHz                          | Bipolar    | 64   |

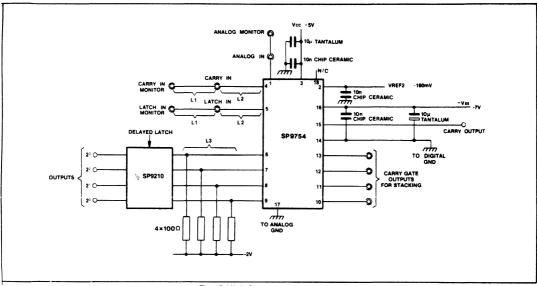

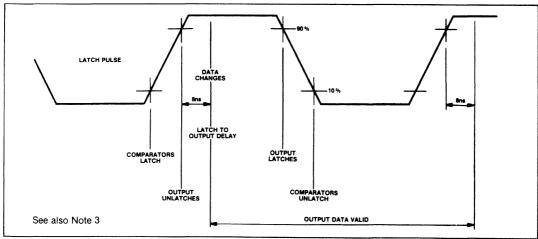

| SP9754   | 4-bit expandable ADC                          | 110MHz                          | Bipolar    | 70   |

<sup>1. 6-</sup> and 8-bit accurate versions available

## Digital to Analog Converters

| A STATE OF THE STA | Function               | Guaranteed Minimum<br>Clock Pate | DAC Max<br>Rise Time          | Pok     |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------|-------------------------------|---------|----|

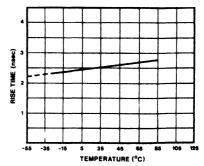

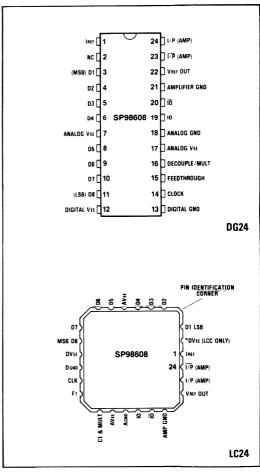

| SP98608                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8-bit multiplying DAC  | 450MHz                           | (10 % - <b>90</b> %)<br>800ps | Bipolar | 75 |

| MV95408                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8-bit video DAC        | 50MHz                            | 5.5ns                         | CMOS    | 80 |

| SP97618C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8-bit graphics DAC     | 200MHz                           | 1.1ns                         | Bipolar | 84 |

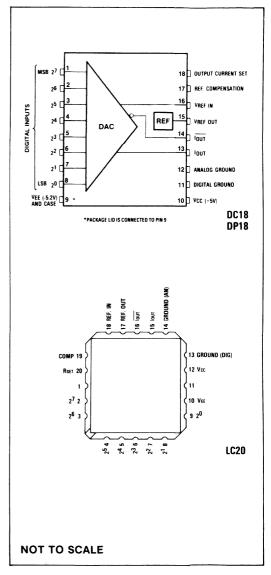

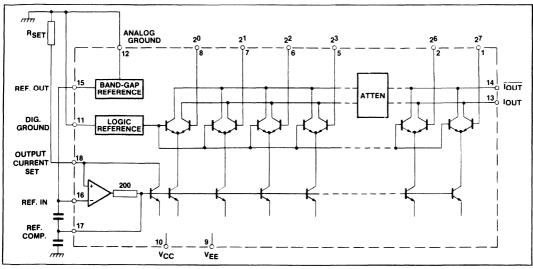

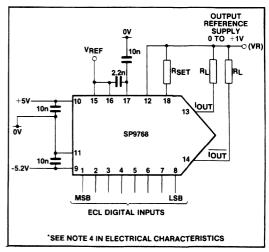

| SP9768                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8-bit multiplying DAC  | 100MHz                           | 2.0ns                         | Bipolar | 90 |

| SP9770                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10-bit multiplying DAC | 50MHz                            | 3.0ns                         | Bipolar | 94 |

# Product index - Data conversion (contd.)

# Comparators

|          |                   |           | 2000 - 1900 - 1900<br>3000 - 1900 - 1900 - 1900 - 1900 - 1900 - 1900 - 1900 - 1900 - 1900 - 1900 - 1900 - 1900 - 1900 - 1900 - 1900 |                   |       |             |         |     |

|----------|-------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|-------------|---------|-----|

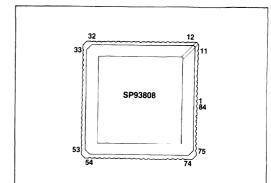

| SP938081 | Octal comparator  | 10V       | $\pm 4 V$                                                                                                                           | $\pm 5 \text{mV}$ | 950ps | 150ps (typ) | Bipolar | 98  |

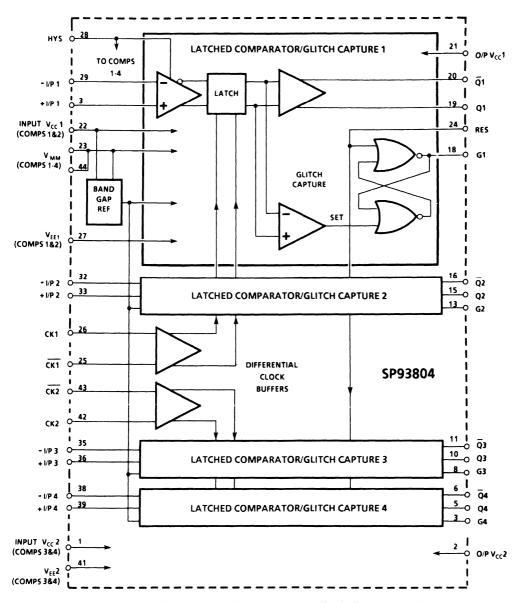

| SP938041 | Quad comparator   | 10V       | $\pm 4V$                                                                                                                            | $\pm 5 \text{mV}$ | 950ps | 150ps (typ) | Bipolar | 107 |

| SP938021 | Dual comparator   | 10V       | ±4V                                                                                                                                 | ±5mV              | 950ps | 150ps (typ) | Bipolar | 116 |

| SP9687   | Dual comparator   | +5V,-5.2V | ±2.5V                                                                                                                               | 5mV               | 3ns   | 1ns (min)   | Bipolar | 125 |

| SP9685   | Single comparator | +5V,-5.2V | $\pm 2.5 V$                                                                                                                         | 5mV               | 3ns   | 1ns (min)   | Bipolar | 130 |

| SP9680   | Single comparator | +5V,-5.2V | $\pm 2.5 V$                                                                                                                         | 6mV               | 4ns   | -           | Bipolar | 135 |

<sup>1.</sup> Adjustable hysteresis, Glitch capture

## **Support**

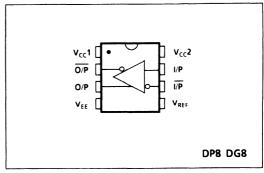

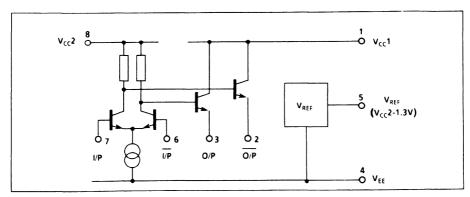

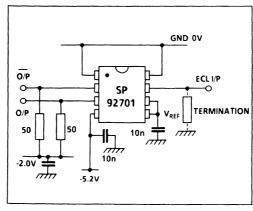

| SP92701 | Single subnanosecond ECL line receiver and driver | -5.2V                       | Bipolar | 137 |

|---------|---------------------------------------------------|-----------------------------|---------|-----|

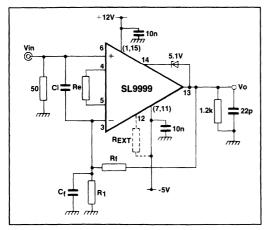

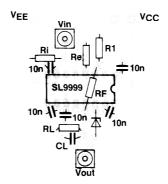

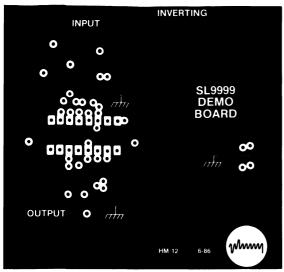

| SL9999  | 400MHz ADC driver operational amplifier           | +9V to +15V/<br>-5V to -15V | Bipolar | 140 |

# Product index -Specialised memory products

First In/First Out Memories

| 100                     | Function 194               | Express 1         | Someth<br>Value |                   | 746 |

|-------------------------|----------------------------|-------------------|-----------------|-------------------|-----|

| MJ2812                  | 32 x 8-bit cascadable FIFO | 2MHz              | 5V              | NMOS1,2           | 151 |

| MJ2812HS                | 32 x 8-bit cascadable FIFO | 5MHz              | 5V              | NMOS1,2           | 156 |

| MJ2813                  | 32 x 9-bit cascadable FIFO | 2MHz              | 5V              | NMOS1,2           | 151 |

| MJ2841                  | 64 x 4-bit cascadable FIFO | 1.75MHz           | 5V              | NMOS1,2           | 161 |

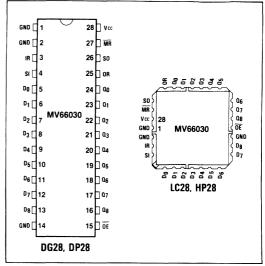

| MV66030-253             | 64 x 9-bit cascadable FIFO | 25MHz             | 5V              | CMOS1             | 164 |

| MV66030-10 <sup>3</sup> | 64 x 9-bit cascadable FIFO | 10MHz             | 5V              | CMOS1             | 164 |

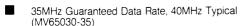

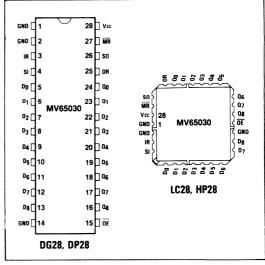

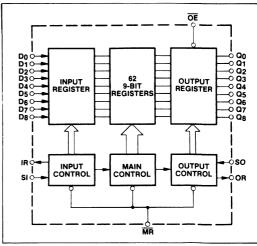

| MV65030-353             | 64 x 9-bit standalone FIFO | 35MHz             | 5V              | CMOS <sup>1</sup> | 171 |

| MV65030-253             | 64 x 9-bit standalone FIFO | 25MHz             | 5V              | CMOS <sup>1</sup> | 171 |

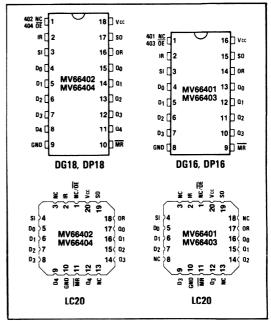

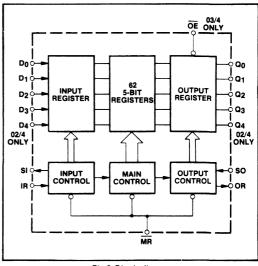

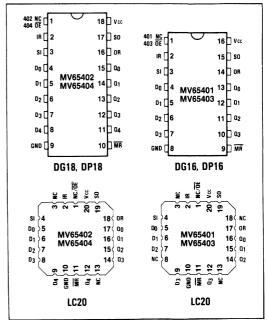

| MV66401-25              | 64 x 4-bit cascadable FIFO | 25MHz             | 5V              | CMOS <sup>1</sup> | 177 |

| MV66401-10              | 64 x 4-bit cascadable FIFO | 10MHz             | 5V              | CMOS <sup>1</sup> | 177 |

| MV65401-35              | 64 x 4-bit standalone FIFO | 35MHz             | 5V              | CMOS <sup>1</sup> | 184 |

| MV65401-25              | 64 x 4-bit standalone FIFO | 25MHz             | 5V              | CMOS <sup>1</sup> | 184 |

| MV66402-25              | 64 x 5-bit cascadable FIFO | 25MHz             | 5V              | CMOS <sup>1</sup> | 177 |

| MV66402-10              | 64 x 5-bit cascadable FIFO | 10MHz             | 5V              | CMOS <sup>1</sup> | 177 |

| MV65402-35              | 64 x 5-bit standalone FIFO | 35MHz             | 5V              | CMOS <sup>1</sup> | 184 |

| MV65402-25              | 64 x 5-bit standalone FIFO | 25MHz             | 5V              | CMOS <sup>1</sup> | 184 |

| MV66403-25 <sup>3</sup> | 64 x 4-bit cascadable FIFO | 25MHz             | 5V              | CMOS <sup>1</sup> | 177 |

| MV66403-10 <sup>3</sup> | 64 x 4-bit cascadable FIFO | 10MHz             | 5V              | CMOS <sup>1</sup> | 177 |

| MV65403-35 <sup>3</sup> | 64 x 4-bit standalone FIFO | 35MHz             | 5V              | CMOS <sup>1</sup> | 184 |

| MV65403-25 <sup>3</sup> | 64 x 4-bit standalone FIFO | 25MHz             | 5V              | CMOS <sup>1</sup> | 184 |

| MV66404-25 <sup>3</sup> | 64 x 5-bit cascadable FIFO | 25MHz             | 5V              | CMOS <sup>1</sup> | 177 |

| MV66404-10 <sup>3</sup> | 64 x 5-bit cascadable FIFO | 10MHz             | 5V              | CMOS <sup>1</sup> | 177 |

| MV65404-353             | 64 x 5-bit standalone FIFO | 35MHz             | 5V              | CMOS <sup>1</sup> | 184 |

| MV65404-25 <sup>3</sup> | 64 x 5-bit standalone FIFO | 25MHz             | 5V              | CMOS <sup>1</sup> | 184 |

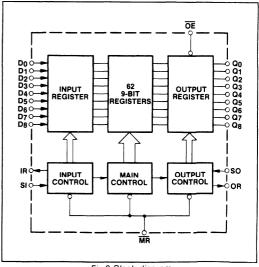

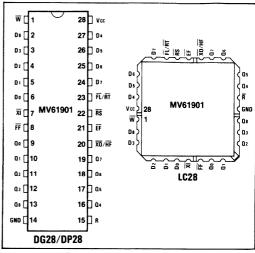

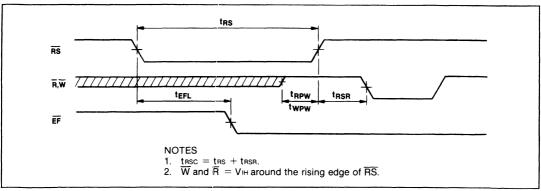

| MV61901-50              | 1K x 9-bit cascadable FIFO | 50ns<br>(access)  | 5V              | CMOS <sup>1</sup> | 190 |

| MV61901-80              | 1K x 9-bit cascadable FIFO | 80ns<br>(access)  | 5V              | CMOS <sup>1</sup> | 190 |

| MV61901-120             | 1K x 9-bit cascadable FIFO | 120ns<br>(access) | 5V              | CMOS <sup>1</sup> | 190 |

| MV61902                 | 1K x 9-bit 'Dipstick' FIFO | 10MHz             | 5V              | CMOS <sup>1</sup> | 201 |

| MV61903                 | 1K x 9-bit 'Parity' FIFO   | 10MHz             | 5V              | CMOS <sup>1</sup> | 210 |

<sup>1.</sup> TTL compatible 2. CMOS compatible 3. With output enable

# Memory Support

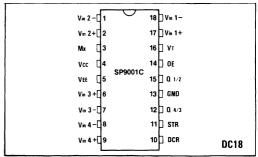

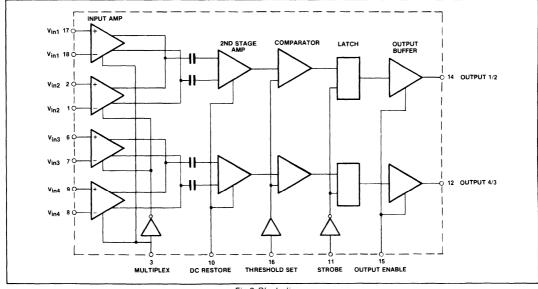

| SP9001C | 4-channel magnetic bubble memory sense amplifier | ±5V | Bipolar | 218 |

|---------|--------------------------------------------------|-----|---------|-----|

# Product index - High speed logic

# Very Fast ECL

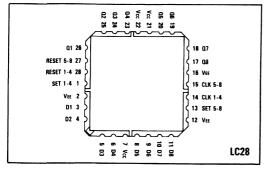

| SP9131  | Dual D-type flip-flop (ultra-fast version of MC10131)       | -5.2V | 520MHz | 227 |

|---------|-------------------------------------------------------------|-------|--------|-----|

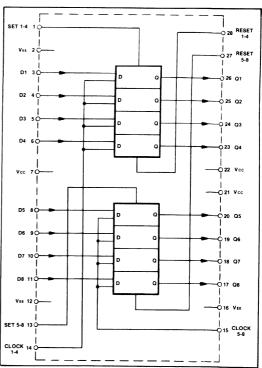

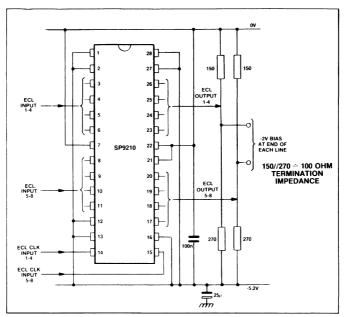

| SP9210  | 8-bit latch (dual 4)                                        | -5.2V | 200MHz | 231 |

| SP16F60 | Dual 4-I/P OR/NOR gate (pin/function compatible with MC1660 | -5.2V | 0.55ns | 235 |

# Standard ECL III

| Voltage controlled oscillator    | +5V or -5.2V                                                                                                                             | 225MHz                                                                                                                                                                               | 150mW                                                                                                                                                                                                                                                                                                                                                             | 237                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dual A/D comparator              | +5V and -5.2V                                                                                                                            | 3.5ns                                                                                                                                                                                | 330mW                                                                                                                                                                                                                                                                                                                                                             | 243                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Voltage controlled multivibrator | -5.2V                                                                                                                                    | 155MHz                                                                                                                                                                               | 130mW                                                                                                                                                                                                                                                                                                                                                             | 252                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Dual 4-I/P OR/NOR gate           | -5.2V                                                                                                                                    | 1ns                                                                                                                                                                                  | 120mW                                                                                                                                                                                                                                                                                                                                                             | 256                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Quad 2-I/P NOR gate              | -5.2V                                                                                                                                    | 1ns                                                                                                                                                                                  | 300mW                                                                                                                                                                                                                                                                                                                                                             | 258                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Quad 2-I/P OR gate               | -5.2V                                                                                                                                    | 1ns                                                                                                                                                                                  | 300mW                                                                                                                                                                                                                                                                                                                                                             | 261                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D-type flip-flop                 | -5.2V                                                                                                                                    | 300MHz                                                                                                                                                                               | 250mW                                                                                                                                                                                                                                                                                                                                                             | 264                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Quad line receiver               | -5.2V                                                                                                                                    | 1.1ns                                                                                                                                                                                | 220mW                                                                                                                                                                                                                                                                                                                                                             | 270                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                  | Dual A/D comparator  Voltage controlled multivibrator  Dual 4-I/P OR/NOR gate  Quad 2-I/P NOR gate  Quad 2-I/P OR gate  D-type flip-flop | Dual A/D comparator +5V and -5.2V  Voltage controlled multivibrator -5.2V  Dual 4-I/P OR/NOR gate -5.2V  Quad 2-I/P NOR gate -5.2V  Quad 2-I/P OR gate -5.2V  D-type flip-flop -5.2V | Dual A/D comparator         +5V and -5.2V         3.5ns           Voltage controlled multivibrator         -5.2V         155MHz           Dual 4-I/P OR/NOR gate         -5.2V         1ns           Quad 2-I/P NOR gate         -5.2V         1ns           Quad 2-I/P OR gate         -5.2V         1ns           D-type flip-flop         -5.2V         300MHz | Dual A/D comparator         +5V and -5.2V         3.5ns         330mW           Voltage controlled multivibrator         -5.2V         155MHz         130mW           Dual 4-I/P OR/NOR gate         -5.2V         1ns         120mW           Quad 2-I/P NOR gate         -5.2V         1ns         300mW           Quad 2-I/P OR gate         -5.2V         1ns         300mW           D-type flip-flop         -5.2V         300MHz         250mW |

# Product List - alpha numeric

| TYPE No.           | DESCRIPTION                                            | PAGE             |

|--------------------|--------------------------------------------------------|------------------|

| The state of       | 2002-20x9-be-accident CFO                              | 151              |

| MJ2812HS           | 5MHz 32 x 8-bit cascadable FIFO                        | 156              |

| MATORS             | 2MHz 32 x 9-bit cascadable FIFO                        | 151              |

| MJ2841             | 1.75MHz 64 x 9-bit cascadable FIFO                     | 161              |

| MYCOUT ATTEMPT AND | HDLC/DMA controller                                    | 17               |

| MV6101             | Dual quadrature counter                                | 26               |

| 100 (01-30         | IK se E-UK casandaya F-PO (Gran apang)                 | 100              |

| MV61901-80         | 1K x 9-bit cascadable FIFO (80ns access)               | 190              |

| MV61901-120        | 1K x 9-bit cascadable FIFO (120ns access)              | 314 1 <b>490</b> |

| MV61902            | 10MHz 1K x9-bit 'Dipstick' FIFO                        | 201              |

| 10 VG 1003         | 10MHz 1K x 9-bit Parity FIFO                           | 210              |

| MV65030-25         | 25MHz 64 x 9-bit standalone FIFO (with output enable)  | 171              |

| Microso-as         | 35MHz 84 x 9-bit standations FIFO (with output enable) | 204 <b>7</b> 1   |

| MV65401-25         | 25MHz 64 x 4-bit standalone FIFO                       | 184              |

| MY05401-85         | 35MHz 64 x 4-bit standalone FIFO                       | 184              |

| MV65402-25         | 25MHz 64 x 5-bit standalone FIFO                       | 184              |

| WY95402-35         | 35MHz 64 x 5-bit standslone FIFO                       | 184              |

| MV65403-25         | 25MHz 64 x 4-bit standalone FIFO (with output enable)  | 184              |

| NOVE 5103-35       | 35MHz 64 x 4-bit standalone FIFO (with output enable)  | 184              |

| MV65404-25         | 25MHz 64 x 5-bit standalone FIFO (with output enable)  | 184              |

| MV05404-35         | 35MHz 64 x 5-bit standalone FIFO (with output enable)  | 184°             |

| MV66030-10         | 10MHz 64 x 9-bit cascadable FIFO (with output enable)  | 164              |

| MV00030-25         | 25MHz 64 x 9-bit cascadable FIFO (with output enable)  | 164              |

| MV66401-10         | 10MHz 64 x 4-bit cascadable FIFO                       | 177              |

| MY98401-25         | 25MHz 64 X 4-bit cascadable FIFO                       | 177              |

| MV66402-10         | 10MHz 64 x 5-bit cascadable FIFO                       | 177              |

| NV60402-25         | 25MHz 84 x 5-bit cascadable FIFO                       | <b>基度177</b> 。   |

| MV66403-10         | 10MHz 64 x 4-bit cascadable FIFO (with output enable)  | 177              |

| 10/00003-25        | 25MHz 64 x 4-bit cascadable FIFO (with output engle)   | 177              |

| MV66404-10         | 10MHz 64 x 5-bit cascadable FIFO (with output enable)  | 177              |

| MV66404-25         | 25MHz 84 x 5-bit cascadable FIFO (with output enable)  | 177              |

| MV95408            | 8-bit 60MHz CMOS video DAC                             | 80               |

| TYPE No. | DESCRIPTION                                          | PAGE |

|----------|------------------------------------------------------|------|

|          |                                                      |      |

| SL9999   | 400MHz ADC driver op. amp.                           | 140  |

|          |                                                      |      |

| SP1650   | ECL III dual ADC                                     | 243  |

|          |                                                      | 050  |

| SP1660   | ECL III dual 4-input OR/NOR gate                     | 256  |

| SP1664   | ECL III quad 2-input OR gate                         | 261  |

|          | Lot III dad I IIIpat Origano                         | 201  |

| SP1692   | ECL III quad line receiver                           | 270  |

|          |                                                      |      |

| SP9001C  | 4-channel magnetic bubble memory sense amplifier     | 218  |

|          |                                                      |      |

| SP9210   | 8-bit 200MHz ECL latch                               | 231  |

|          |                                                      |      |

| SP9685   | Single 3ns latched comparator                        | 130  |

| SP9754   | 4-bit 100MHz expandable ADC                          | 70   |

| 3P9/34   | 4-bit Toolvin iz expandable ADO                      | 70   |

| SP9768   | 8-bit 100MHz multiplying DAC                         | 90   |

|          |                                                      |      |

| SP9920   | 50Mbit Manchester decoder with idle code detect, for |      |

|          | fibre optics/LAN                                     | 36   |

|          |                                                      |      |

| SP9960   | Encoder/LED driver for fibre optics                  | 29   |

|          |                                                      |      |

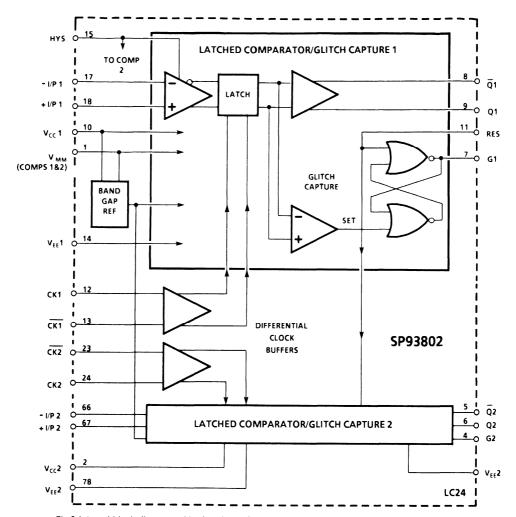

| SP93802  | Dual sub-nanosecond comparator                       | 116  |

|          |                                                      |      |

| SP93808  | Octal sub-nanosecond comparator                      | 98   |

|          |                                                      |      |

| SP97308E | 8-bit 30MHz flash ADC, ECL outputs                   | 51   |

| 0007560  | 8-bit 110MHz flash ADC                               | 45   |

| SP97508  | 0-DIL TIUMITZ HASH ADC                               | 45   |

| SP98608  | 8-bit 450MHz multiplying DAC                         | 75   |

| 3F 30000 | o bit foom is manipiying bito                        | 7.5  |

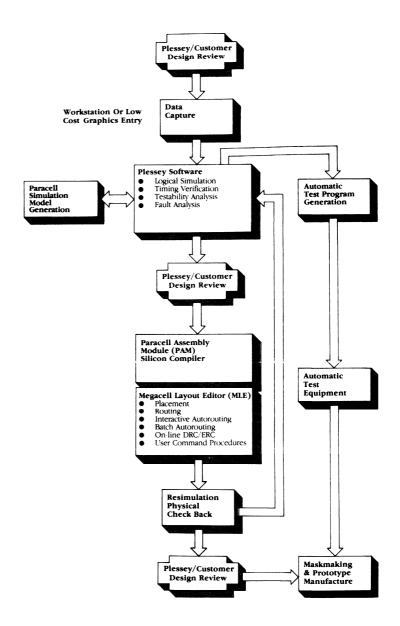

# Semi-Custom design

For more than a decade Plessey Semiconductors has led and consistently advanced the state of the art in semi-custom technology.

This leadership has been based on the use of comprehensive design software, Plessey Design System (PDS). PDS is independent of both technology and function in that Gate Arrays and cell based designs using CMOS or Bipolar can be developed.

PDS is supported on a DEC \*VAX (VMS) based system. However, Plessey supports Daisy, Valid and Mentor workstations, which are all interfaced into PDS, thereby offering an easy design route to meet your needs and costs.

These support routes offer the user the maximum flexibility in their design. However, Plessey also offers a 'turnkey' design function where we will complete the design from start to finish.

We offer a complete range of CMOS and Bipolar processes to meet all requirements of speed, power, packing density and cost and a very comprehensive range of through-hole, surface mount and pin grid array packages.

## Gate Array Families

Plessey offers a complete range of Gate Array families, in both CMOS and ECL, for cost-effective, fast turn-round projects - see tables below.

#### **CLA 3000 SERIES (CMOS)**

- Double layer metal

- 4 micron channel length

- 2.8ns typ. gate delay

- 20MHz system clock

- Fully auto-routed

- 3V to 6V power supply

- Static protected I/O

- Static protected if

- Military screening

- >90 % utilization of gates

#### PRODUCT FAMILY:

|         | Gates | I/O | Power |

|---------|-------|-----|-------|

| CLA31XX | 840   | 40  | 4     |

| CLA33XX | 1440  | 52  | 4     |

| CLA35XX | 2400  | 64  | 4     |

|         |       |     |       |

#### **ELA 60000 (ECL)**

- High performance: 1GHz

- 180ps typ. gate speed

- ECL 10K, ECL 100K, TTL and

- CMOS compatible

- Programmable speed/power

- Full military operation

#### PRODUCT FAMILY:

| · Amilei. |                            |

|-----------|----------------------------|

| Gates     | Pads                       |

| 660       | 48                         |

| 1400      | 68                         |

| 2900      | 96                         |

| 4500      | 120                        |

|           | <b>Gates</b> 660 1400 2900 |

#### CLA 5000 SERIES (CMOS)

- Double layer metal

- 2 micron channel length

- 1.2ns typ. gate delay

- 40MHz system clock rate

- Fully auto-routed

- 3V to 6V power supply

- Static protected I/O

- Military screening

- >90% utilization of gates

#### PRODUCT FAMILY:

|         | Gates | I/O | Power                            |

|---------|-------|-----|----------------------------------|

| CLA51XX | 640   | 36  | 4                                |

| CLA52XX | 1232  | 48  | 8                                |

| CLA53XX | 2016  | 64  | 8                                |

| CLA54XX | 3060  | 80  | 8                                |

| CLA55XX | 4408  | 96  | 16                               |

| CLA56XX | 5984  | 112 | 16                               |

| CLA57XX | 7104  | 128 | 16                               |

| CLA58XX | 8064  | 144 | 16                               |

| CLA59XX | 10044 | 160 | 16                               |

|         |       |     | Consideration of the Section Co. |

## Plessey MEGACELL

PLESSEY MEGACELL offers the ASIC designer the opportunity to move to VHSIC gate complexities without losing the simplicity of gate array design methods.

MEGACELL also offers design freedom and product innovation through creative design.

## Cell Library

Four types of library elements are available giving functional, dynamic, and physical design flexibility:

**Microcells** are modular size cells of simple logic functions (gates and flip-flops) similar to those in current standard logic families.

**Macrocells** comprise a user-library of building-blocks (e.g. 74 Series TTL) compiled from Microcells to speed up design entry.

Paracells are cells which can be parameterised through their regular composition (e.g. ROM, RAM, PLA). The simple netlist cell code is auto-compiled into a physical entity requiring very little design effort for these types of cells.

Supracells are large fixedfunction cells pre-designed to replicate or improve existing VLSI standard functions. Many standard products can be incorporated into the Supracell concept.

## Design Route

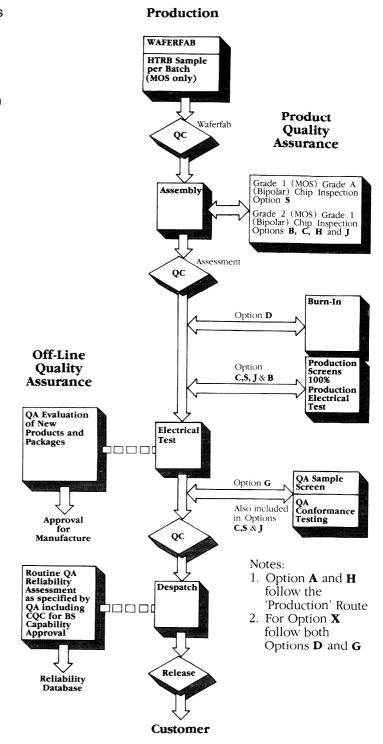

# The Quality Concept

Plessey Semiconductors makes MOS and bipolar integrated circuits of various types for commercial, professional and military customers. However, a single common management system is used to control the manufacturing processes which is planned to meet the requirements of BS9000 and DEF-STAN 05-21. Plessey Semiconductors can supply product meeting the requirements of MIL-STD-883C.

This means that all products benefit from the use of reliable processes with strict controls of individual stages and overall quality control. Where customers require even higher quality grades this is achieved by additional screening and testing but all grades are produced on the same manufacturing processes operating under consistent control systems.

At Plessey Semiconductors, quality and reliability are built into the product by rigorous control of all processing operations and by minimizing random defects. Process management involves extensive documentation of procedures, recording of batch data, employment of extensive traceability procedures and the provision of appropriate equipment and facilities.

## Screening Options

Plessey Semiconductors currently offers integrated circuits screened to any of nine options. The ways in which these options are exercised during the manufacturing cycle are shown in the Reliability Assessment Flow diagram opposite.

OPTION A. **Standard Plessey Product.** The devices are 100% electrically tested and have 100% physical inspection applied prior to despatch. AQL for electrical tests is as low as 0.1% on volume product. AQL for physical inspection is 0.4%.

OPTION B is **Plessey Hi-Rel Level B** screening. This involves 100% screening, including 160 hour burn-in (ref. 446/SQ/05742, Issue 1).

OPTION C is the **MIL-STD-883C Class B.** This involves screening, including burn-in, 100 \(^1/4\) hot and cold testing plus Groups A, B, C and D Conformance testing.

OPTION D (MOS only) is as for Standard Plessey Product but with 100% static burn-in. 20 hours, 125°C, maximum operating voltage.

OPTION G (MOS only) is a conformance (lot-by-lot) assessment using the methods of **BS9400**. This gives customer assurance that every batch has been assessed by QA. The **BS6001** sampling plan is used with the AQL level from BS9400 (no BS detail specification involved).

OPTION H is **STACK 0001**, which embodies the purchasing recommendations of a leading group of telecommunications equipment manufacturers.

OPTION J (MOS only) is a **BS9450 Assessment Level S2** capability, for which we are currently seeking approval. This specification is recommended for devices destined for applications where the system will be highly stressed, both electrically and physically, or where repair would be difficult.

OPTION S is a **MIL-STD-883C Class S** requirement for space applications, submarine repeaters and satellites where repairs, if not impossible would be extremely difficult and expensive. This involves even more comprehensive screening than Class B and more onerous lot conformance testing.

OPTION X (MOS only) is the same as Option G with regard to lot-by-lot conformance but carried out in conjunction with Option D.

# Technical Data

1. Data communications

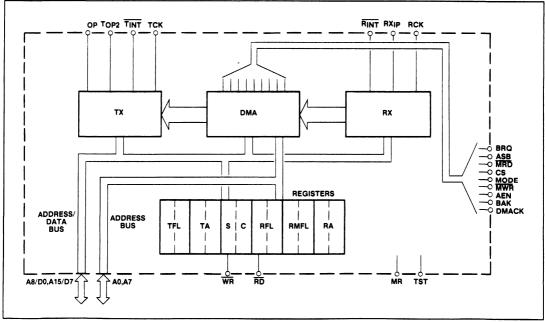

# MV6001 HDLC/DMA CONTROLLER

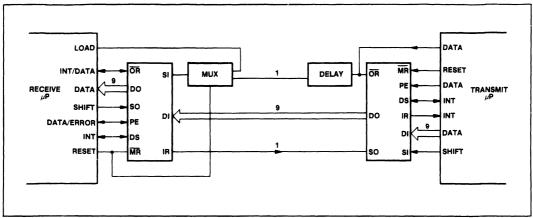

The MV6001 is a combined HDLC transceiver and DMA controller capable of providing serial communications at rates up to 128K bits/second, and handling direct memory access clock rates up to 8MHz.

#### **FEATURES**

- Data Rates up to 128K Bits/s

- DMA Rate up to 8MHz

- Low Power CMOS

- Simple Interfacing to Popular 8-Bit Processors

- Frame Length up to 2K Bytes

- Low Host-Processor Overhead

- Conforms to ECMA40 and Related Standards (CCITT X.25, X.75, 1.440, ISO3309, ANSI X3.66, FED-STD 1003, FIPS71)

#### **APPLICATIONS**

- ISDN Terminals

- LANs

- X25 p.s.s. Networks

#### ORDERING INFORMATION

MV6001 B0 DP (Commercial Plastic DIP)

MV6001 B0 DG (Commercial Ceramic DIP)

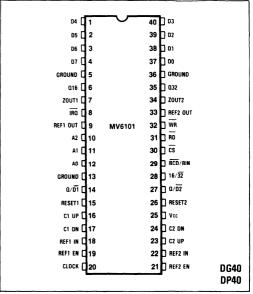

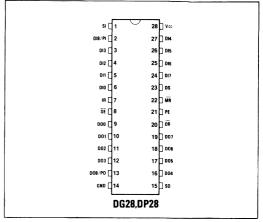

Fig.1 Pin connections - top view

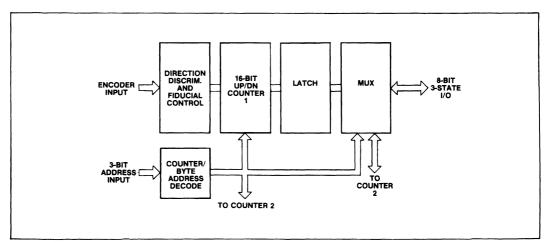

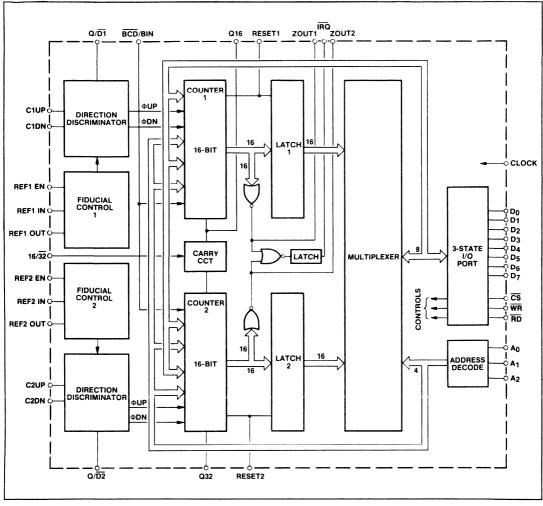

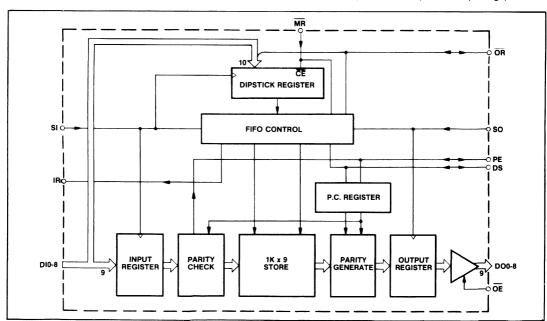

Fig.2 Block diagram

#### MV6001

#### PIN DESCRIPTION

| Pin No. | Name                    | I/O | Function                                                                                                                                                                                                                                            |

|---------|-------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,10,20 | GND                     |     | <b>0V supply.</b> All 3 pins must be connected.                                                                                                                                                                                                     |

| 2 - 9   | <b>A</b> 0 - <b>A</b> 7 | I/O | <b>Address Bus.</b> Output for memory $A_0$ - $A_7$ addressing. Input for register addresses $A_0$ - $A_3$ .                                                                                                                                        |

| 11      | TST                     | 1   | Test Enable. Tie to GND for normal operation.                                                                                                                                                                                                       |

| 12 - 19 | A8/D0 - A15/D7          | I/O | Data Bus/High Order Address. Multiplexed data and address bus.                                                                                                                                                                                      |

| 21      | Тор2                    | 0   | Transmitter Out. Alternative output to TXop. This output is not affected by loop back (see Operating Notes - LOOPBACK).                                                                                                                             |

| 22      | TINT                    | 0   | <b>Transmitter Interrupt.</b> An interrupt is generated whenever transmission of a frame is ended, either following the last FCS byte of a complete frame of when an abort sequence is transmitted. The interrupt is reset by the control register. |

| 23      | RINT                    | 0   | Receiver Interrupt. An interrupt is generated whenever a frame is received. The interrupt is reset by the counter register.                                                                                                                         |

| 24      | ASB                     | 0   | Address Strobe. Strobes the Address High byte from the Data/Address Bus into an external latch.                                                                                                                                                     |

| 25      | AEN                     | 0   | Address Enable. Enables the external address latch.                                                                                                                                                                                                 |

| 26      | RXIP                    | ı   | Receiver Input. Serial HDLC data input, clocked in by RCK.                                                                                                                                                                                          |

| 27      | RCK                     | ı   | <b>Receiver Data Clock.</b> Provides clock to the receiver section, frequency should be at the required data rate, this need not necessarily the the same as the transmit data rate.                                                                |

| 28      | TCK                     | 1   | <b>Transmitter Data Clock.</b> This input provides a clock signal for the transmitter section and should be set to the desired transmit data rate.                                                                                                  |

| 29      | ТХор                    | 0   | Transmitter output. Main transmitter output for serial data.                                                                                                                                                                                        |

| 30      | MODE                    | 1   | <b>Bus Control Mode Select.</b> Controls the polarity of BAK and BRQ. MODE = Vcc gives active LOW, MODE = GND gives active HIGH.                                                                                                                    |

| 31      | WR                      | 1   | Write Register. Loads data from data bus into register addressed by Ao - A3.                                                                                                                                                                        |

| 32      | RD                      | 1   | Read Register. Reads addressed register onto data bus.                                                                                                                                                                                              |

| 33      | DMACK                   | 1   | <b>DMA Clock</b> . This input provides clock to the DMA section. The DMA clock rate should be at least ten times the sum of the transmit and receive data rates.                                                                                    |

| 34      | CS                      | 1   | Chip Select. Enables RD and WR inputs.                                                                                                                                                                                                              |

| 35      | BAK                     | 1   | <b>Bus Acknowledge.</b> Input from processor relinquishing control of bus. See pin 30, Bus Mode Select.                                                                                                                                             |

| 36      | BRQ                     | 0   | <b>Bus Request.</b> Output to processor requesting the bus for a DMA cycle. See pin 30, Bus Mode Select.                                                                                                                                            |

| 37      | MR                      | ŀ   | Master Reset. Resets everything.                                                                                                                                                                                                                    |

| 38      | MWR                     | 0   | <b>Memory Write.</b> This is a three-state output to write data into memory during DMA cycles.                                                                                                                                                      |

| 39      | MRD                     | 0   | Memory Read. 3-state output to read data from memory during DMA cycles.                                                                                                                                                                             |

| 40      | Vcc                     |     | $+5$ V $\pm$ 10% supply.                                                                                                                                                                                                                            |

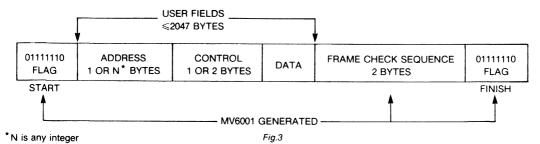

#### **HDLC FRAME CONSTRUCTION**

Fig.3 shows the construction of an HDLC frame. The start and finish of the frame are determined by FLAGS (the binary pattern 01111110). To prevent spurious recognition of flags in the user fields, the transmitter automatically inserts a '0' after five successive '1's. The inserted '0's are removed by the receiver, and hence are not seen by the user. Each HDLC frame contains a 2 byte frame check sequence produced by a cyclic redundancy generator in the transmitter. This sequence is checked by the receiver to validate the frame.

There are two other sequences which have specific meanings - IDLE and ABORT. The IDLE state is the transmission of at least 15 continuous '1's without inserted zeros. ABORT is 7 to 14 consecutive '1's without inserted zeros sandwiched between two zeros.

#### **FUNCTIONAL DESCRIPTION**

The MV6001 consists of four main sections; transmitter, receiver, DMA unit and register bank. Each of the transmitter, receiver and DMA unit have their own clocks running at the required data rates. There are no restrictions on the relative training between transmit and receive clocks, the DMA clock rate should be greater than ten times the sum of the transmit and receive clock rates.

#### **Transmission**

In its steady state the transmitter produces a continuous stream of FLAGS until the control register is loaded with a transmit instruction. The transmitter then, at intervals, requests the DMA unit to fetch a byte of data. This is then transferred from the system memory via the data bus to the transmitter. (If the DMA unit should fail to fetch a byte of data by the time the next request arrives then an under-run will occur and the transmitter will transmit an ABORT sequence). Data is converted into a serial stream with inserted zeros after five ones, and the 16-bit frame check sequence is appended at the end of each frame. As soon as the last bit of the FCS has been clocked out, the Tint output goes low to inform the processor that transmission has ended.

#### INITIALISATION

To start transmission, two items of information are required - the start address for the data to be transmitted, and the length of the user fields are loaded into the TA and TFL registers respectively, after which the transmit enable bit (Do) can be set at any time to start transmission. Once a transmission has been started, the only way it can by stopped is to set the abort bit (Do). The transmitter will then transmit the abort sequence followed by flags. Transmitter reset (Dz) resets the transmitter interrupt  $\overline{T}$  int, clears the TA and TFL registers and bits Do and Do of the status register. Transmitter reset is disabled during a transmission.

#### Interrupt

A transmitter interrupt (Tint) is generated whenever a transmission ceases, the status register can then be read to check if the frame was aborted or not. The interrupt is reset by writing a transmitter reset to the control register. NB. The status register must be read before a transmitter reset as this will alter the contents of the status register.

#### **Status**

The transmitter has two status bits - transmitting data ( $D_0$ ) and abort ( $D_1$ ). The transmitting data bit should always be low after  $T_{\text{INT}}$  signifying that transmission is ended. The abort bit will be high whenever a frame is aborted either by an abort instruction to the control register, or internally due to an under-run.

#### Reception

The receiver accepts serial data, removes inserted zeros and checks the frame check sequence. For each byte of data received, the receiver section generates a DMA request to transfer the data to memory. If the DMA controller fails to make the transfer before the next request from the receiver, then the receiver will drop out and give a receiver interrupt with the code in the status register for overrun. If the number of bytes received reaches the number in the receive maximum frame length register the receiver will drop out and give an interrupt with the code in the status register for frame too long.

#### Initialisation

The RA register (2 bytes) is loaded with the address where the first received byte of data is to be stored. The RMFL register (11 bits) is loaded with the maximum number of bytes in the user fields plus 3 bytes (+2 bytes for the FCS, +1 byte because an interrupt will occur when the frame length is equal to the length set by the number in the register).

#### Control

The receiver has two control bits in the control register, receive enable (D<sub>3</sub>) and receive reset (D<sub>4</sub>). Once the RA and RMFL registers have been loaded, the receive enable bit can be set at any time to allow the receiver to receive a frame. Once set, the receive enable bit cannot be overwritten and receive reset is disabled until a frame has been received.

Receiver reset will reset the RINT interrupt bit, registers RFL, RMFL, RA and bits D2 - D7 of the status register.

#### MV6001

#### Interrupt

A receive interrupt (Rint) is generated whenever a frame is received. The status register can then be read to check the status of the received frame. The interrupt is reset by writing a receiver reset to the control register. Since the reset will clear the receiver bits in the status register, the register must be read before writing the reset to the control register.

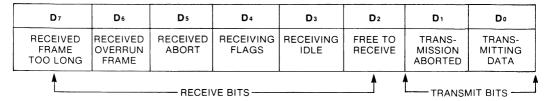

#### **Status**

The receiver uses bits  $D_2$  -  $D_7$  of the status register (see Figs. 5 and 6). A valid frame is indicated by both 'overrun' ( $D_6$ ) and 'frame too long' ( $D_7$ ) bits being high. Following  $\overline{R}_{1NT}$  the 'free to receive' bit ( $D_2$ ) should be low, indicating that a frame has been received. The abort, overrun and long frame bits will be set according to the state of the frame received. The flag ( $D_4$ ) and idle ( $D_3$ ) bits monitor the incoming signal continuously even when the receiver is disabled.

#### Frame Length Register

Having received a frame and read the status register, the received frame length can be read from the RFL register. The frame length is given as an eleven bit number and includes the 2 FCS bytes in the count. The register should be read before a receiver reset.

#### Loopback

Bit D7 of the control register, the loopback bit is provided for testing purposes. When the bit is set high an internal

connection is made between the transmitter output and receiver input. The main transmitter output (TXoP) transmits IDLE (transmitted data is always available on ToP2). The receiver is clocked from TCK. The loopback bit will respond to every write to the control register.

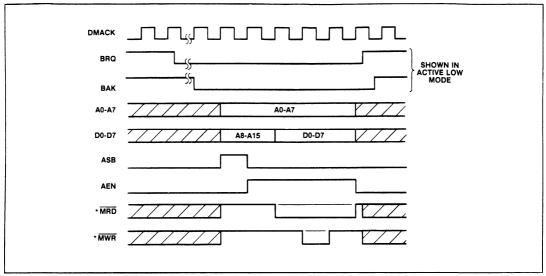

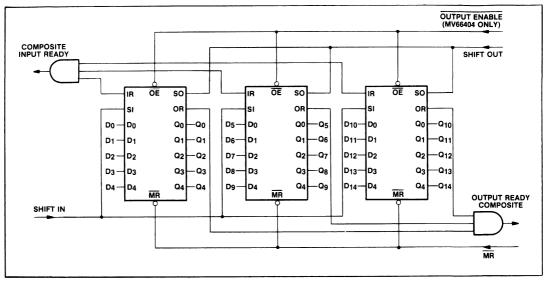

#### **Direct Memory Access (Fig.11)**

All data transfers to or from memory are carried out by the DMA controller. Each time it receives a request from the transmitter or receiver it will carry out one DMA cycle, i.e. only one byte is transferred at a time. Clashes between transmitter and receiver are resolved in favour of the receiver, otherwise operation is on a first come, first served basis.

#### Registers

Fig.7 shows the addresses for the various instruction and status registers. All registers are readable from and writable to except for S, C and RFL. The S and C registers have the same address, which one is accessed is determined by whether a read (status) or write (control) operation is carried out. Transmitter registers should not be written to when transmitting (except to ABORT a frame), likewise receiver registers should not be written to when receiving. The TA and RA registers update continuously during transmission and reception respectively, giving the next address to be read from or written to.

| <b>D</b> 7 | D <sub>6</sub> | <b>D</b> 5 | D4      | Dз      | D <sub>2</sub> | <b>D</b> 1 | Do       |

|------------|----------------|------------|---------|---------|----------------|------------|----------|

| LOOPBACK   | DON'T          | DON'T      | RECEIVE | RECEIVE | TRANSMIT       | TRANSMIT   | TRANSMIT |

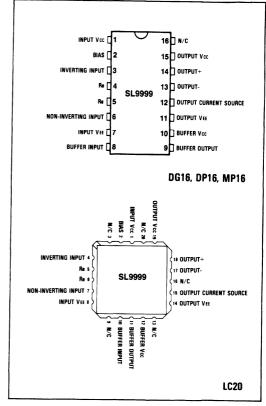

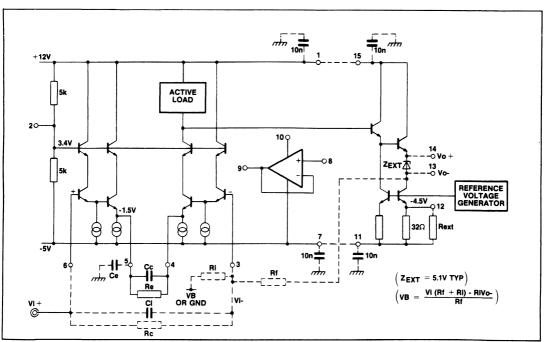

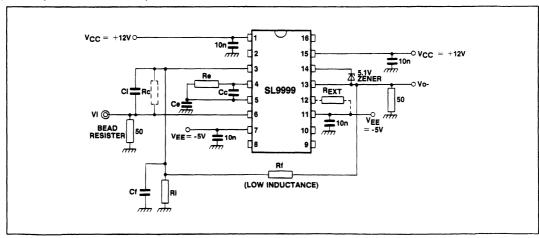

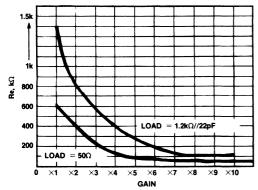

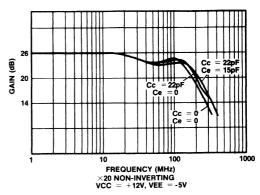

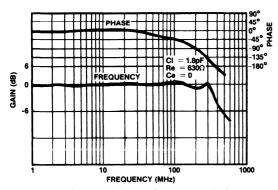

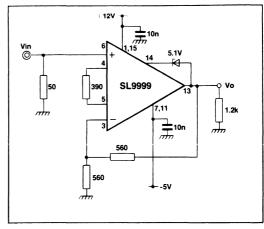

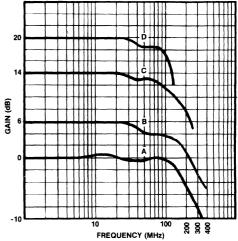

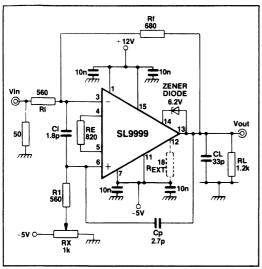

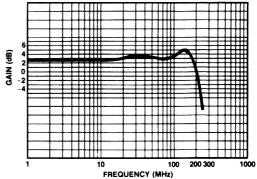

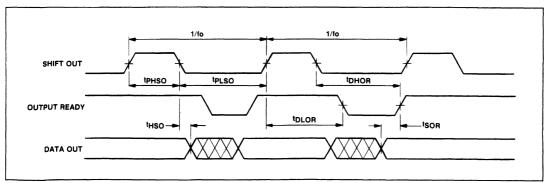

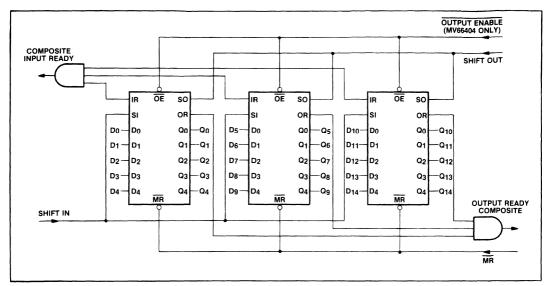

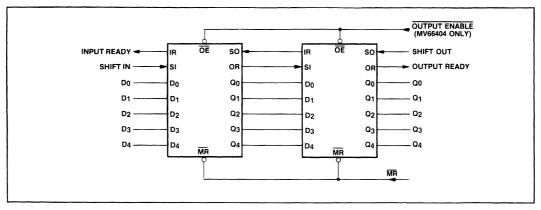

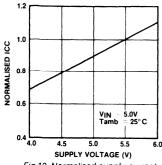

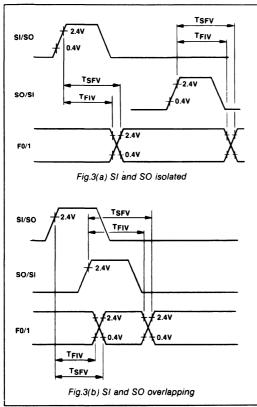

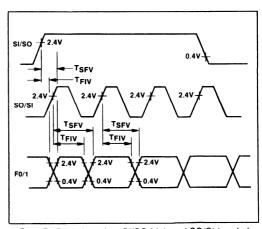

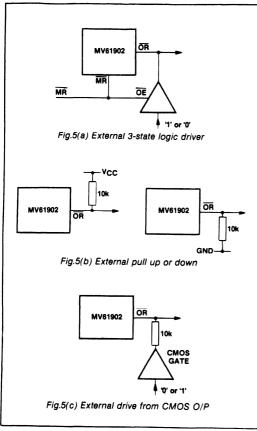

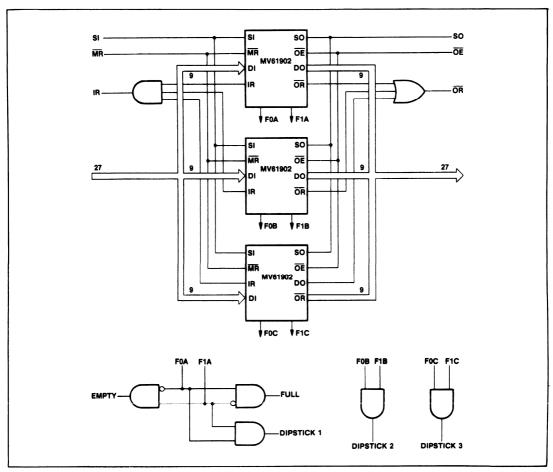

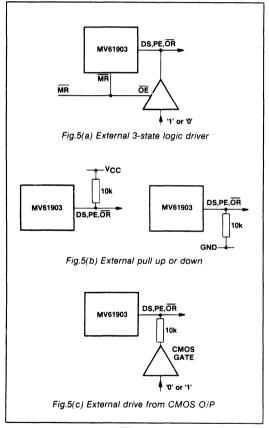

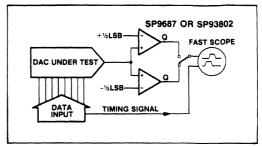

| ENABLE     | CARE           | CARE       | RESET   | ENABLE  | RESET          | ABORT      | ENABLE   |